CPU Components and Functions: A-Level Computer Science

Learn about the Fetch-Decode-Execute cycle, Von Neumann architecture, ALU, Control Unit, and CPU registers for OCR A-Level Computer Science.

The Central Processing Unit (CPU)

A-Level Computer Science (OCR Specification)

What is the CPU?

The 'Brain' of the Computer: Responsible for processing all data and instructions.

Fetch-Decode-Execute: The fundamental cycle used to process instructions sequentially.

Performance: Measured in Clock Speed (GHz), Core count, and Cache size.

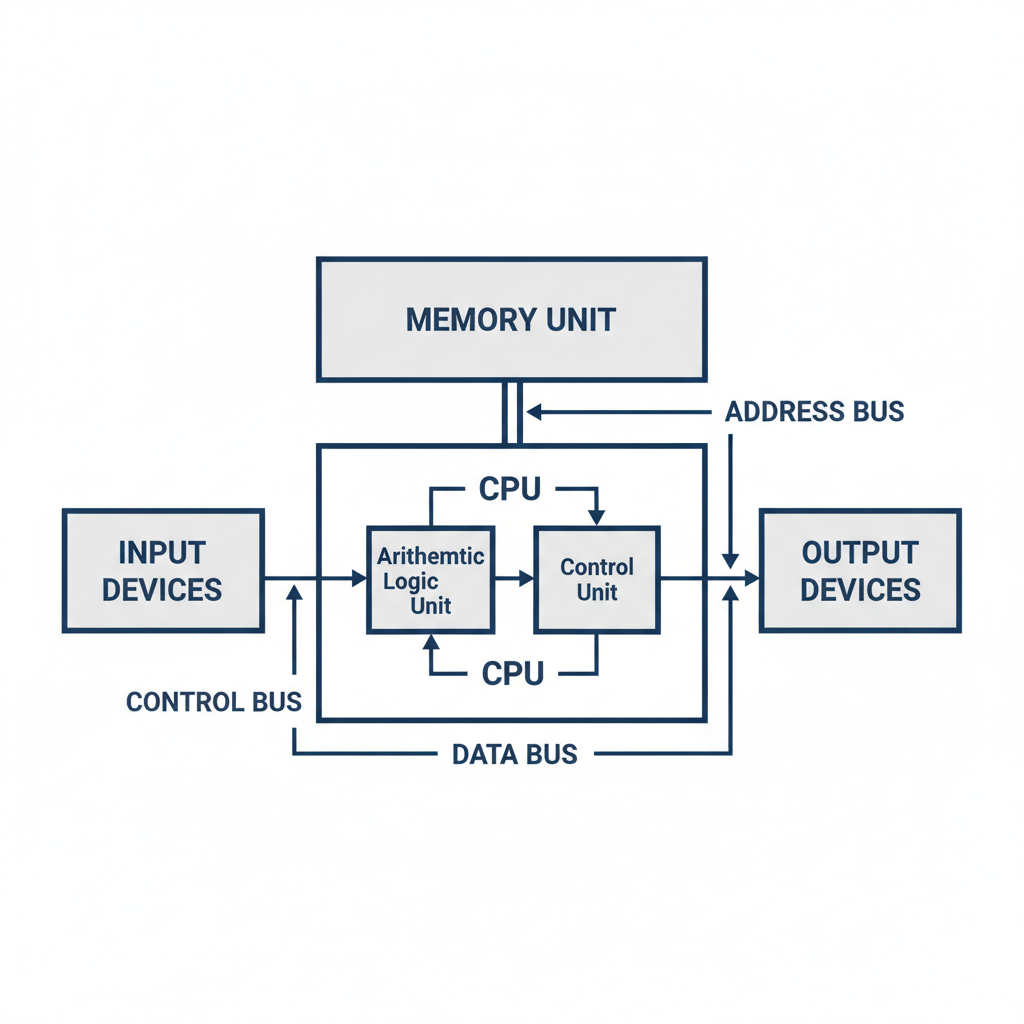

Von Neumann Architecture

Stored Program Concept: Instructions and data are stored in the same main memory.

Sequential execution of instructions.

Single control unit managing the Fetch-Decode-Execute cycle.

Arithmetic Logic Unit (ALU)

Performs Arithmetic Operations: Addition (+), Subtraction (-), Multiplication (*), Division (/).

Performs Logic Operations: Logical comparisons (AND, OR, NOT, XOR).

Acts as the gateway through which all calculations pass.

Control Unit (CU)

Control: Manages the execution of instructions and flow of data inside the CPU.

Decoding: Interprets the instructions fetched from memory.

Signals: Sends control signals to other components (ALU, Memory, I/O) to coordinate actions.

Registers: Speed Hierarchy

Registers are tiny, ultra-fast storage locations inside the CPU. They are much faster than Cache or RAM.

Key Registers (1/3)

Program Counter (PC)

Stores the memory address of the NEXT instruction to be fetched.

Accumulator (ACC)

Stores the intermediate results of calculations performed by the ALU.

Key Registers (2/3)

Memory Address Register (MAR)

Holds the address of the current instruction or data being fetched from memory.

Memory Data Register (MDR)

Holds the actual data or instruction temporarily after fetch or before write.

Key Registers (3/3)

Current Instruction Register (CIR)

Holds the current instruction while it is being decoded and executed.

Since the MDR changes frequently, the instruction is copied to the CIR to maintain stability during decoding.

System Buses

1. Data Bus (Bi-directional)

Carries data and instructions between the Processor and Memory.

2. Address Bus (Uni-directional)

Carries the memory address of the next instruction or data item.

3. Control Bus (Bi-directional)

Carries control signals (e.g., Read/Write) from the CU to other components.

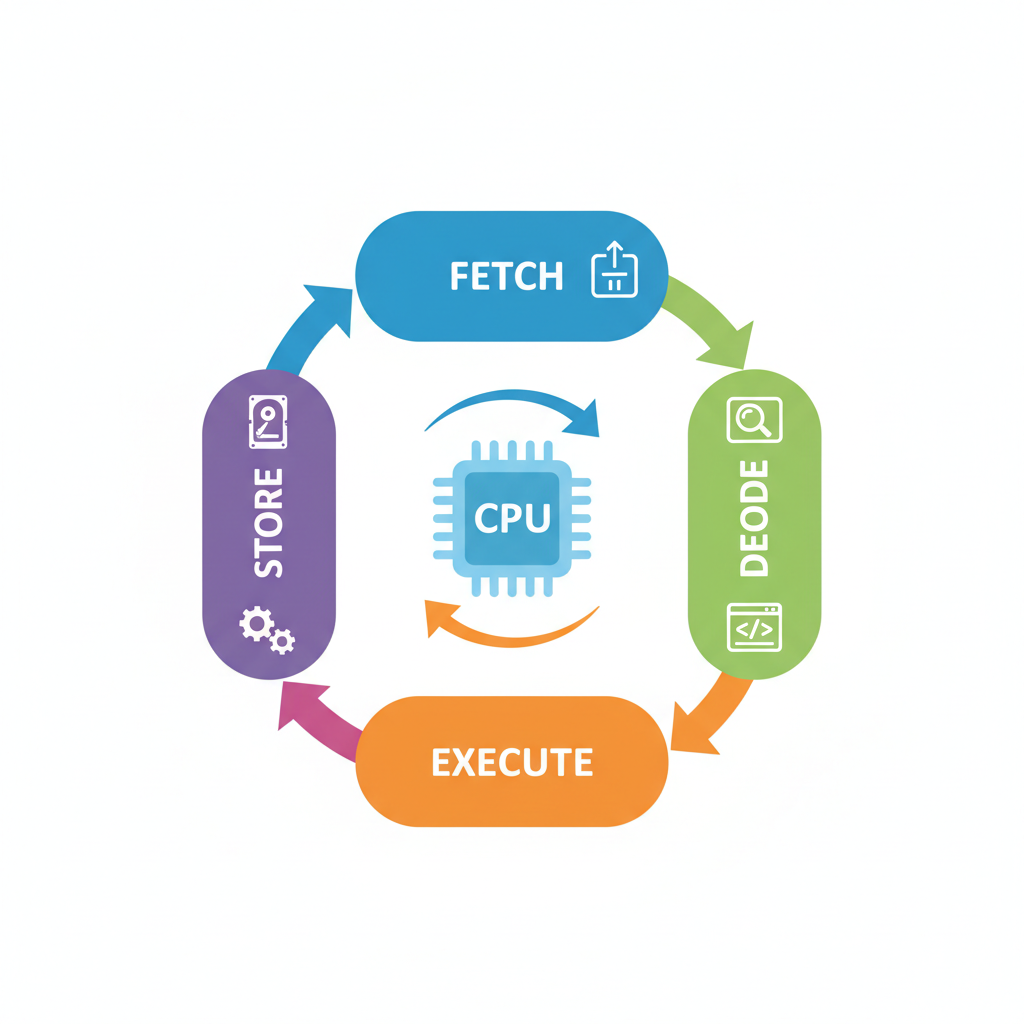

Fetch-Decode-Execute Cycle

FETCH: Address from PC -> MAR. Instruction copied from Memory -> MDR -> CIR.

DECODE: Control Unit interprets the instruction in the CIR.

EXECUTE: Process performed (e.g., calculation in ALU, data transfer).

Summary

CPU: The 'brain' processing instructions using Fetch-Decode-Execute.

Components: ALU (math/logic), CU (control), Registers (fast memory).

Key Registers: PC, ACC, MAR, MDR, CIR are essential for the cycle.

Buses: Address, Data, and Control buses connect components.

- computer-science

- cpu-architecture

- von-neumann

- fetch-decode-execute

- ocr-specification

- registers

- alu