ML-Based Macro-Modeling for SAR ADC Analog IC Design

Learn how Machine Learning-Based Macro-Modeling (MMM) achieves 3600x speedup over SPICE in SAR ADC performance estimation with less than 1% error.

MMM: Machine Learning-Based Macro-Modeling

Accelerating Performance Estimation for Linear Analog ICs and ADC/DACs

Yishuang Lin, Yaguang Li, Meghna Madhusudan, et al.

METHODLY

#ffffff

The Bottleneck: Analog Design Automation

SPICE simulations are computationally expensive, slowing down optimization loops (days to weeks).

Existing ML Models (Flat P2M): Require massive training data (thousands of simulations) and lack reusability.

Symbolic Analysis & MOR: Limited to small or linear circuits; struggle with ADCs/DACs.

METHODLY

#1a237e

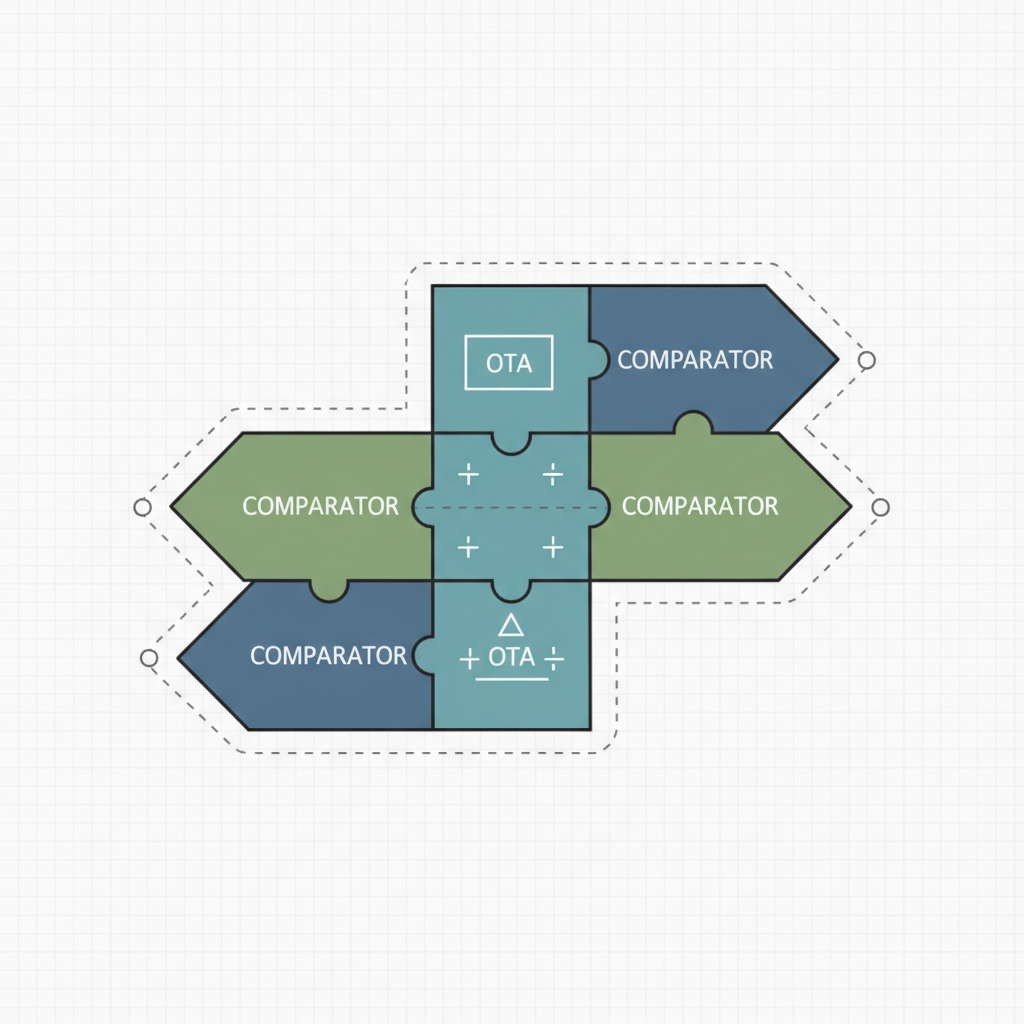

The MMM Solution: Hierarchical Macro-Modeling

Decompose large circuits into standard reusable sub-circuits (e.g., OTA, Comparator).

Train Once, Reuse Everywhere: Models for sub-circuits are trained independently and assembled for system estimation.

Handling Complexity: Separate handling for Loading Effects, Feedback Loops, and Variable Inputs.

METHODLY

#1a237e

Methodology: Linear Analog ICs

DC Voltage Modeling: ML models estimate DC operating points (considering loading effects).

Parametric Transfer Function: H(s) coefficients are predicted by ML models based on DC points and device sizes.

Pole/Zero Analysis

METHODLY

#1a237e

Methodology: Time-Domain for ADCs

Unlike linear ICs, ADCs require discrete time-step evaluation to capture dynamic behavior.

Sequential Propagation: Output V(t) depends on Input V(t), Input V(t-1), and Output V(t-1).

Key Sub-circuits: Comparators and Encoders are modeled individually and linked.

Performance Output: FFT performed on time-domain waveform to extract SFDR and SNDR.

METHODLY

#ffffff

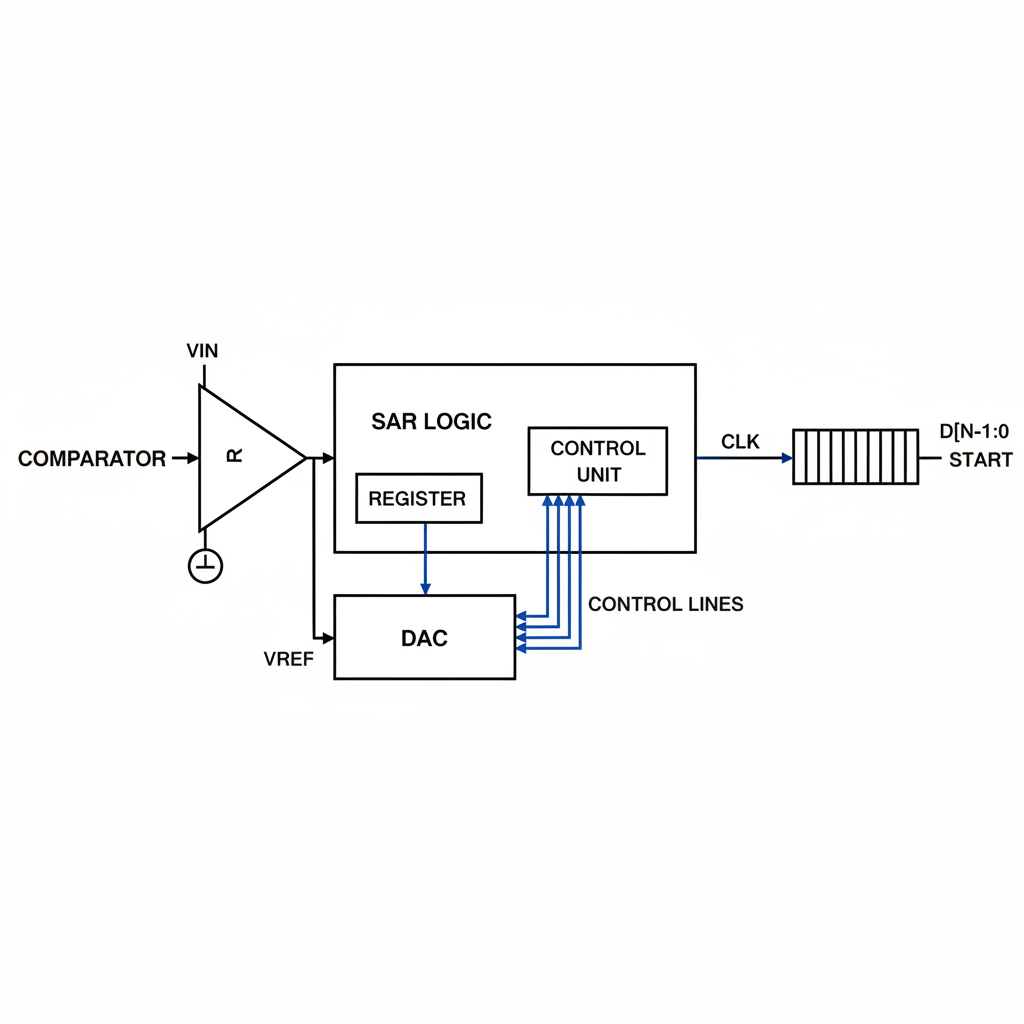

Applying MMM to SAR ADCs

While initial results cover Flash/Pipeline ADCs, the MMM framework is naturally suited for Successive Approximation Register (SAR) architectures.

Comparator: Modeled via MMM Time-Domain interface (proven accurate in Flash results).

Capacitive DAC: Modeled similarly to Weighted Resistor DACs (linear passive network).

SAR Logic Loop: Digital feedback handled by system-level netlist assembly.

METHODLY

#1a237e

Result: Modeling Accuracy

MMM achieves significantly lower error rates (<1%) compared to flat ANN and GNN approaches.

METHODLY

#1a237e

Huge Reduction in Data Preparation Cost

For an 8-bit Flash ADC, MMM reduced simulation needs from 40 days to just 9.6 hours (due to sub-circuit reuse).

METHODLY

#1a237e

Inference Speed: Replacing SPICE

MMM is orders of magnitude faster than SPICE for full-system verification.

8-bit ADC Evaluation Time: SPICE ~ 30 minutes vs MMM < 0.1 second.

METHODLY

#1a237e

Conclusion & Future Work

MMM enables scalable, fast, and reusable performance modeling for Analog/Mixed-Signal ICs.

Achieved >1700x speedup in data prep and >3600x in inference speed over SPICE with <1% error.

Future Focus: Expanding the library for SAR ADCs and complex feedback loops in high-speed data converters.

METHODLY

#ffffff

- analog-ic-design

- machine-learning

- sar-adc

- spice-simulation

- circuit-modeling

- eda-automation